# A-SSCC 2025 Review

서강대학교 전자공학과 석박통합과정 박종민

## Session 12 Ultra high-speed transceiver

2025 ASSCC Session 12는 총 4편의 논문이 발표되었다. "Beyond 100Gb/s"의 공통된 흐름 속에 초고속 데이터 전송을 위한 여러 연구들이 수신기 2편, 광통신 1편, 송신기 1편로 나누어 소개가 되었다. 특별히 PAM-4/PAM-8/QAM와 같은 고차변조기법에 필수적인 정밀한 Equalization 기법들이 소개되었고, 높은 선형성 및 에너지 효율에 초점이 맞추어지며, 단순한 Data rate 확대가 아닌 완성도 높은 송수신 시스템을 요구하는 산업의 흐름을 볼 수 있다. 그 중 Receiver와 관련된 논문 2편을 살펴보고자 한다.

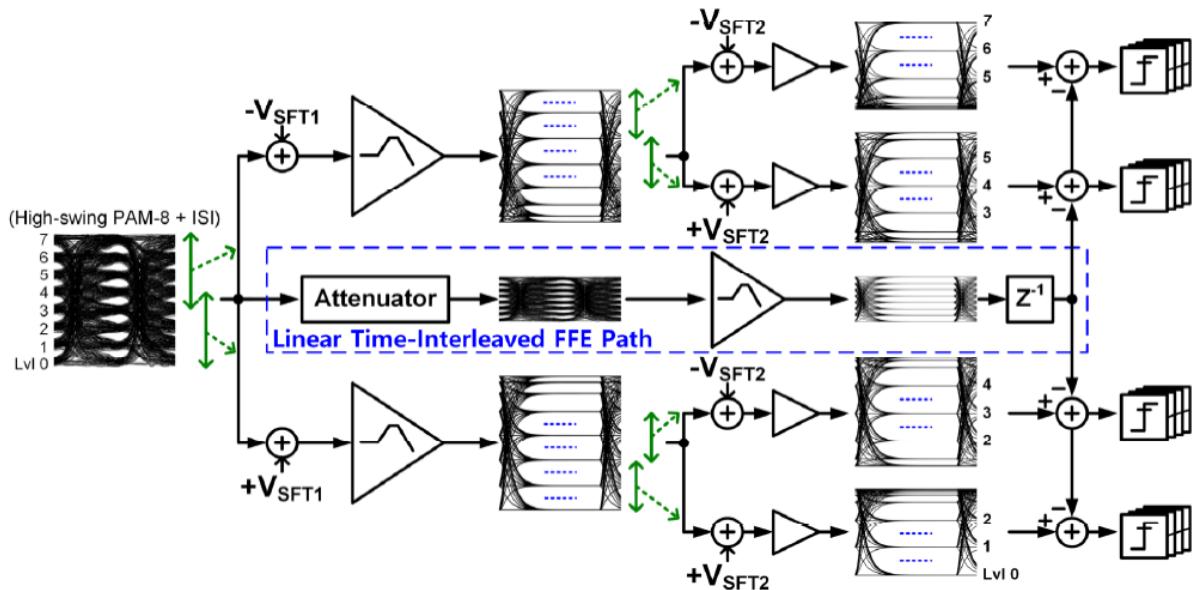

**#12-1** 본 논문은 한양대학교에서 발표한 논문으로 108Gb/s의 PAM-8 Receiver의 높은 linearity를 보장하기 위해 Multi-path CTLE+FFE구조의 Equalization system을 제안한다. High-swing으로 입력되는 PAM-8 signal에서의 linearity를 만족하기 위해 Linear time-interleaved FFE가 도입되었으며, High-swing에 대한 linearity 확보를 위한 Attenuator, ISI를 보상하기 위해 입력신호의 레벨을 Sampling하는 Track and Hold circuit(TAH) 그리고 FFE의 coefficient를 조절하기 위한 VGA로 구성이 되어있으며, TAH에서는 timing margin을 확보하기 위해 75% Duty Cycle clock signal을 활용하였다. 한편 CTLE의 구조에서는 Amplifier를 활용한 4-way sub-ranging technique을 통해 8개의 signal level을 PAM-3형태로 나누어 결과적으로 동일한 간격의 Signal level를 만족하는 high-linearity PAM-8 Equalizing System을 구현하였다. 구현된 시스템을 통해 1.4V의 차동입력 신호에 대하여 1.95pJ/bit의 입력전압 대비 높은 전력효율을 보였고 Nyquist frequency에서 10.7dB의 loss 특성을 가진 channel에 대하여 1E-7의 BER을 만족하며 기존 CTLE+2-tap FFE system 대비 개선된 BER특성을 달성했다.

[그림 1] 4-way sub-ranging CLTE + Linear Time-Interleaved FFE의 구성

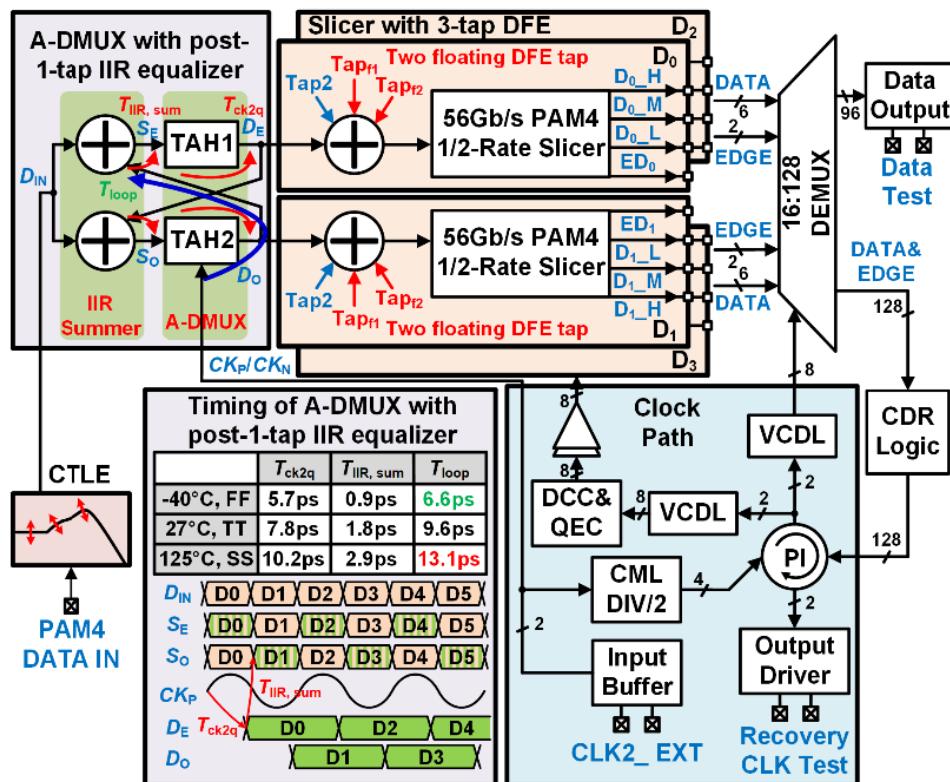

#12-2 는 시안 자오톱 대학교에서 발표한 논문으로 IIR Equalizer와 3-tap Direct DFE를 이용한 time-interleaved 방식의 112Gb/s PAM4 Receiver를 소개한다. 100G급 PAM4 signal에 활용되는 기존 mixed-signal receiver는 DFE의 timing margin 확보의 어려움 및 Clock signaling의 복잡도로 인해 Short-reach 기반의 높은 Data rate에 적용하는 데에 한계가 있었다. 이를 해결하기 위해 Post-1-tap IIR summer와 High-linearity Track and Hold circuit(TAH)를 활용한 1:2 Analog DEMUX를 구성하여 DFE가 가지고 있는 1-tap timing budget을 완화하고, loop-unrolled 구조에서 발생하는 추가적인 파워소모를 줄였다. 이후 long tail로 발생하는 잔여 ISI의 미세 보정을 위해 tap-2 direct DFE와 2 floating tap direct DFE를 활용하여 넓은 bandwidth에서 ISI를 보정할 수 있도록 하였다. 제안된 방식을 활용하여 Nyquist frequency에서 28.4dB의 loss특성을 보이는 channel에서 1E-12수준의 BER 및 1.32pJ/bit의 에너지 효율을 달성하며, channel loss에 대한 에너지효율 FoM인 0.046pJ/bit/dB의 에너지 효율을 달성했다.

[그림 2] 112Gb/s time-interleaved PAM4 RX의 Architecture

## 저자정보

### 박종민 석박통합과정 대학원생

- 소속 : 서강대학교

- 연구분야 : Reference-less CDR/High-Speed Wireline Interface

- 이메일 : park\_john@naver.com

- 홈페이지 : <https://sc.sogang.ac.kr/melab>

# A-SSCC 2025 Review

단국대학교 파운드리공학과 석사과정 임재영

## Session 22 Advanced Timing Recovery

이번 A-SSCC 2025의 Session 22에서는 Advanced Timing Recovery를 주제로 고속, 저전력 시스템에서의 클록 생성 및 복구 과정에서 발생하는 timing jitter, reference spur, phase noise 누적, 그리고 lock 안정성 문제를 다루는 5편의 논문이 발표되었다. 본 세션의 논문들은 subsampling, duty-cycle 제어, injection-locked 동작, 시간 영역 처리 기법 등을 활용하여 timing recovery 성능을 제한하는 요인들을 구조적으로 해결하는 접근을 제시한다. 다음에서는 이 중 timing recovery 메커니즘을 서로 다른 관점에서 다루는 #22.1, #22.2, #22.4 논문의 구조와 동작 방식을 중심으로 정리한다.

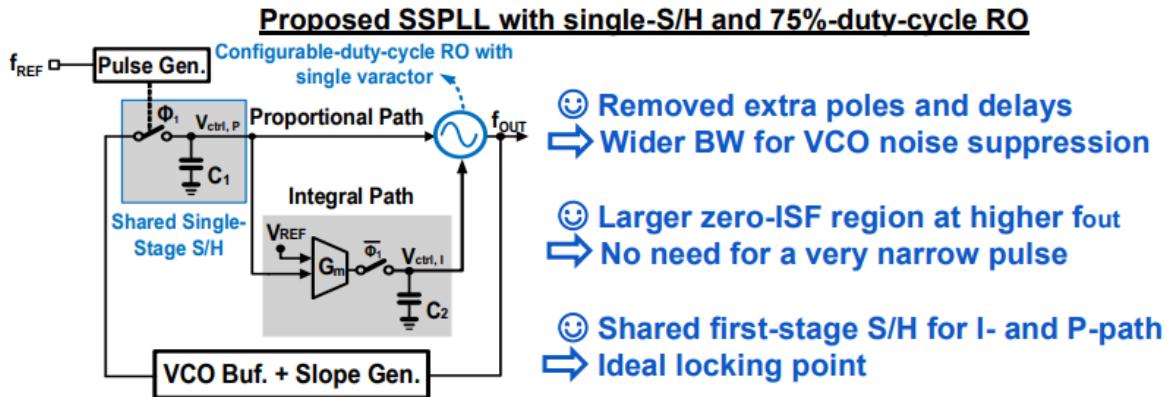

**#22-1** 본 논문은 일본 도쿄대학교에서 발표한 논문으로, RO 기반 subsampling PLL에서 발생하는 reference spur와 timing jitter의 발생 메커니즘을 구조적으로 다룬다. 기존 subsampling PLL에서는 reference clock을 이용해 VCO 출력을 직접 샘플링함으로써 timing jitter를 줄이는 구조가 사용되어 왔다. 이때 RO 기반 PLL을 적용하면 LC 기반 구조 대비 회로 집적도 측면에서 이점이 있으나, 일반적인 50% duty-cycle RO에서는 reference spur의 크기가 duty-cycle과 pulse width에 민감하게 의존하며, timing jitter와 spur 간의 trade-off가 발생한다. 또한 기존 subsampling PLL에서는 I-path와 P-path가 서로 다른 sample-and-hold(S/H) 경로를 사용함에 따라 샘플링 시점 불일치로 인한 timing mismatch가 발생할 수 있다. 이를 완화하기 위한 방법으로 multi-stage S/H 구조나 보정 회로가 사용되어 왔으나, loop 복잡도가 증가하고 추가적인 timing 오차 요인이 생긴다. 본 논문에서는 이러한 문제를 고려하여 configurable duty-cycle ring oscillator를 사용하는 subsampling PLL 구조를 제안하였다. RO의 duty-cycle을 가변적으로 조절함으로써 reference spur의 크기를 구조적으로 제어할 수 있도록 하였으며, spur 억제와 timing jitter 간의 균형을 조절한다. 또한 기존 two-stage S/H 구조 대신 single-stage S/H 구조를 적용하고, I-path와 P-path가 shared S/H를 통해 동일한 샘플링 시점을 공유하도록 구성하였다. 이를 통해 경로 간 timing mismatch를 제거하고 loop 동작 시 발생하는 timing 오차를 줄인다. 측정 결과, 제안된 PLL은 2.6GHz 출력에서 reference spur -70dBc 와 RMS jitter 186fs를 달성하였다.

[그림 1] 제안된 single-S/H 와 75% duty-cycle RO가 적용된 SSPLL

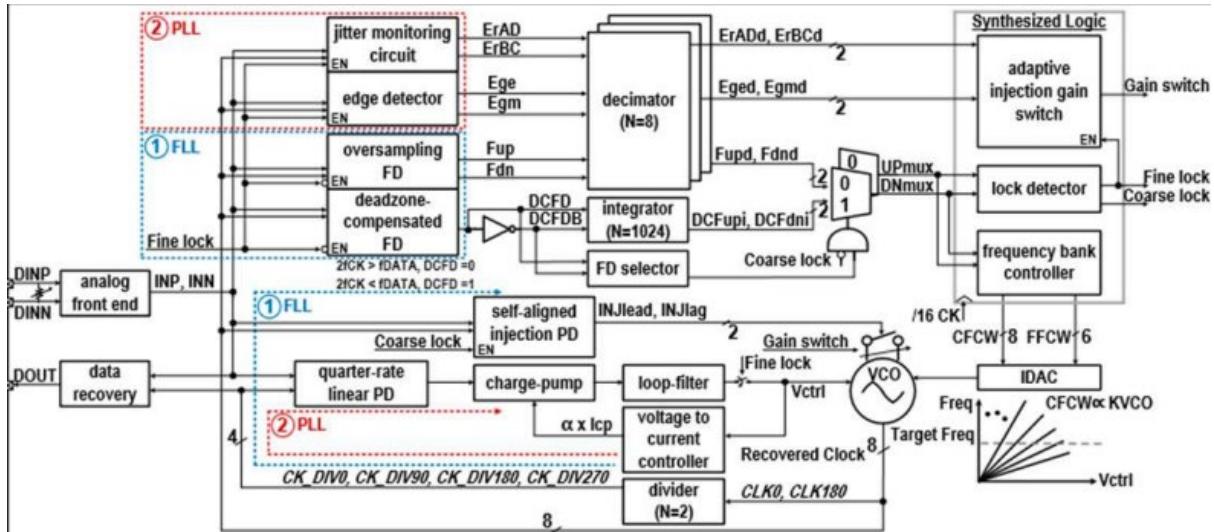

#22-2 본 논문은 대한민국 성균관대학교와 삼성전자에서 발표한 논문으로, reference-less 환경에서 timing lock 안정성 문제를 해결하기 위한 CDR 구조를 제안하였다. 기존 reference-less CDR에서는 입력 데이터 스트림을 이용한 injection-locked 동작이 널리 사용되어 왔으나, 입력 데이터의 jitter 및 PVT 변화에 따라 injection 조건이 쉽게 변하면서 timing lock이 불안정해질 수 있다. 특히 고정된 injection gain을 사용하는 경우, 초기 lock을 위한 충분한 pull-in과 steady-state에서의 안정적인 timing 정렬을 동시에 만족시키기 어렵다. 이를 보완하기 위해 본 논문에서는 dual-loop 구조의 reference-less CDR를 제안하였다. 제안된 구조에서는 주파수 복구를 담당하는 frequency detection 경로와 injection 위상 정렬을 담당하는 경로를 분리하여 구성함으로써, timing recovery 과정에서 각 경로의 역할을 명확히 구분한다. 또한 데이터 에지의 기울기를 이용하는 Injection Pulse Detection(IPD) 기법을 적용하여 injection 조건을 판단한다. injection 과정에서의 timing 안정성을 확보하기 위해 Adaptive Injection Gain Switching(AIGS) 기법이 도입되었으며, lock 상태에 따라 injection gain을 변경함으로써 초기 lock 구간에서는 충분한 injection을 제공하고 steady-stage에서는 timing disturbance를 줄인다. 제안된 CDR은 5Gb/s부터 12.5Gb/s까지의 데이터 속도 범위에서 안정적인 timing lock 동작을 보였으며, 12.5㎱/L 기준 PLL 모드에서 약 14.9mW의 전력 소모를 나타낸다.

[그림 2] adaptive injection gain switching을 적용한 제안된 reference-less CDR 구조

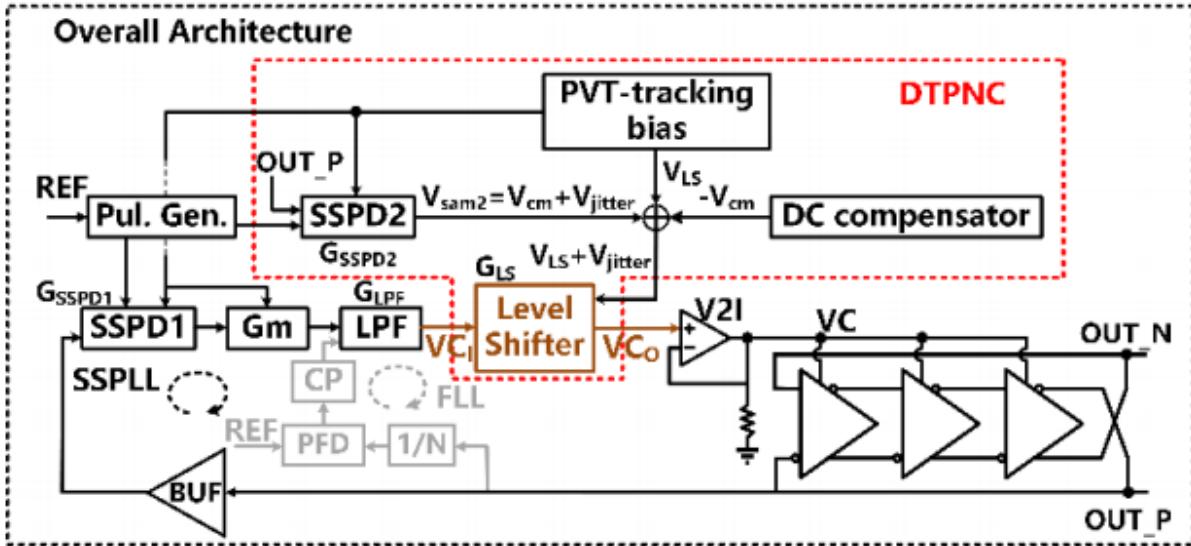

**#22-4** 본 논문은 RVCO 기반 PLL에서 발생하는 multi-phase timing jitter 누적 문제를 다룬다. RVCO 기반 PLL에서는 다상 클록을 생성하는 과정에서 각 phase의 phase noise가 누적되며, PVT 변화에 따라 phase 간 mismatch가 발생하여 clock generation 성능이 제한된다. 기존의 phase noise 저감 기법은 아날로그 보정 회로나 복잡한 calibration 절차를 요구하는 경우가 많다. 본 논문에서는 이러한 한계를 고려하여 Discrete-Time Phase Noise Cancellation(DTPNC) 기법을 적용한 RVCO 기반 SSPLL 구조를 제안하였다. 제안된 구조에서는 RVCO 출력의 phase 정보를 시간 영역에서 샘플링하고, 이를 이용해 timing noise 성분을 디지털 방식으로 제거한다. 이를 통해 아날로그 영역의 추가적인 보정 회로 없이 timing jitter를 줄이는 접근을 취한다. 또한 dual mismatch adjustment를 통해 다상 경로에서 발생하는 불일치를 단계적으로 보정하고, adaptive gain mismatch adjustment 기법을 함께 적용하여, multi-phase 경로 간 gain mismatch로 인한 timing 불균형을 완화한다. 이를 통해 PVT 변화에 따른 timing jitter 변화를 완화한다. 측정 결과, 제안된 SSPLL은 2.4GHz 출력주파수에서 FoM\_jitter -247.4dBc/Hz를 나타낸다.

[그림 3] Discrete-Time Phase Noise Cancellation을 적용한 제안된 RVCO 기반 SSPLL의 전체구조

## 저자정보

임재영 석사과정 대학원생

- 소속 : 단국대학교

- 연구분야 : clock generators

- 이메일 : lgy72250338@dankook.ac.kr

- 홈페이지 : <https://sites.google.com/dankook.ac.kr/acs-lab>